Topic: DMD0161

SR - Shift Register

The Shift Register (SR) instruction shifts BITs through a predefined number of BIT locations. These BIT locations can be a range of BITs, a single Word or DWord, or a range of Words or DWords.

The Shift Register can only shift Bits through the specified range, it cannot be used to shift Byte, Word or DWord values. Refer to the FIFO example in the Move Range (MOVER) instruction on how to shift non-Bit values.

Input Legs:

The Shift Register (SR) instruction has the following three ladder logic input legs:

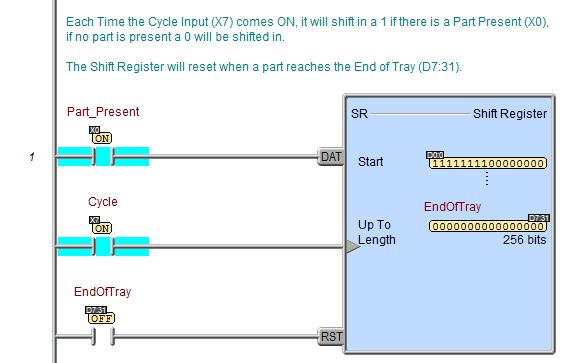

The first ladder logic input leg (DAT) is the Data signal. This determines the value (one or zero) that will enter the shift register.

If the input logic is ON a value of 1 will

be placed in the starting location of the shift register with the next

transition of the Clock signal.

If the input logic is OFF a value of 0 will be placed in the starting location

of the shift register with the next transition of the Clock signal.

The second ladder logic input leg is the Clock signal. The gray triangle

at the right end of an input leg indicates the input is edge triggered![]() Each time the input logic transitions from OFF to ON this instruction will execute. With each execution, this instruction will run to completion even if the input logic transitions to OFF before the instruction completes. meaning that each OFF-to-ON transition of the Clock signal will shift

all of the bits in the shift register one position and move the Data leg's

value into the first shift register bit location.

Each time the input logic transitions from OFF to ON this instruction will execute. With each execution, this instruction will run to completion even if the input logic transitions to OFF before the instruction completes. meaning that each OFF-to-ON transition of the Clock signal will shift

all of the bits in the shift register one position and move the Data leg's

value into the first shift register bit location.

The third ladder logic input (RST) is the Reset signal. When ON, the Reset signal resets all bit positions in the shift register locations to zero.

Parameters:

Note: Use the F9 key or click the 'three dot box' at the right edge of the parameter field to open the Default Element Selection Tool (the Element Picker or the Element Browser) or use the Down-Arrow key (Auto-Complete) on any parameter field to see a complete list of the memory locations that are valid for that parameter of the instruction.

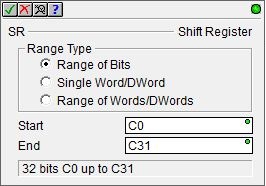

Range Type - specifies the

memory locations that will be used by the Shift Register instruction.

Select one of the following three options for the Range Type:

Range of BITs - specifies a range of contiguous BIT memory locations. When using this memory type the following restrictions apply:

The range must be at least 8 BITs long the range must be multiples of 8 BITs in length.

The maximum range is 2048 BITs.

The range must start at beginning of an 8-bit boundary and end at the end of an 8-bit boundary, for example: C0 - C7 is valid, C0 - C10 is not valid.

Ignore any bits at the end if a multiple of 8 bits is not required in the application.

The direction the BITs will shift is determined by order of the values you enter, for example: C0 - C15 shifts Up, and C15 - C0 shifts Down.

The range can be any writable bit location.

Single Word / DWord - specifies a single Word (16 bit) or single DWord (32 bit) location. When using this memory type the following restrictions apply:

The direction the BITs will shift is always Up, for example: if you select D0, the BITs will shift from D0:0 Up to D0:31.

This can be any writable Word or DWord numeric location.

Range of Words / DWords - specifies a range of contiguous Word or DWord locations. When using this memory type the following restrictions apply:

The maximum number of contiguous Word locations is 128.

The maximum number of contiguous DWord locations is 64.

The direction the BITs will shift is determined by order of the values you enter, for example: V0 - V3 shifts Up from V0:0 to V3:15, and V3 - V0 shifts Down from V3:15 to V0:0.

This can be any writable Word or DWord numeric location.

Start - if Range of Bits or Range of Words / DWords is selected this entry specifies the first memory location to use. If Single Word / DWord is selected, this is the single memory location to use. This can be any writable Bit or Word / DWord location.

End - if Range of Bits or Range of Words / DWords is selected this entry specifies the last memory location to use. This can be any writable Bit or Word / DWord location.

Status Display:

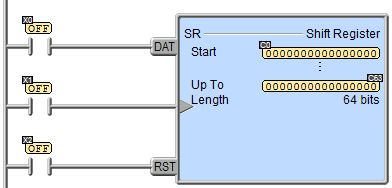

The status display of the Shift Register will display as many of the registers being used as possible. If the full range of the registers cannot be displayed in the instruction, only the first and last registers will be displayed.

This configuration uses bits C0 to C15, status for all 16 bits can be displayed in the instruction.

This configuration uses bits C0 to C63, status for all 64 bits cannot be displayed, only the first 16 bits and the final 16 bits are displayed.

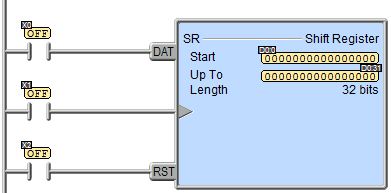

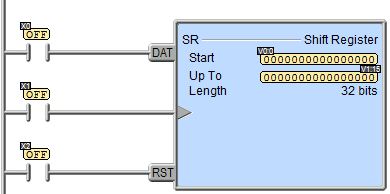

This configuration uses a single DWord D0, status for all 32 bits can be displayed in the instruction.

This configuration uses Words V0 and V1, status for all 32 bits can be displayed in the instruction.

This configuration uses DWords D0 to D9, status for all 320 bits cannot all be displayed, only the first 16 bits of D0 and the final 16 bits of D9 are displayed in the instruction.

See Also:

SR - Shift Register

Example: